-

Lecture 20 (Latches & Flip-Flop)디지털 회로개론 2021. 12. 16. 03:19728x90

Latch

latch는 일시적인 저장 장치 입니다. (2가지 상태로 되어있습니다)

출력이 반대쪽 입력으로 연결되어 있습니다.

왼쪽의 latch는 input이 active-HIGH (SET-RESET) Latch 입니다. NOR gate로 이루어져 있습니다.

오른쪽의 latch는 input이 active-LOW (SET-RESET) Latch 입니다. NAND gate로 이루어져 있습니다.

각 게이트의 출력이 반대쪽 게이트의 입력에 연결됩니다. 이것은 입력과 출력이 연결되어있어 연속 을 가지고 있습니다.

1. input들과 Q 출력 둘다 HIGH 이면 기본상태입니다.

2. Q 출력으로 부터 R' 인풋이 HIGH이면 G2의 출력은 LOW 입니다.

3. G2 의 출력이 LOW가 G1의 입력으로 들어가므로 G1의 출력은 HIGH가 됩니다.

Q 출력이 HIGH이면 래치가 SET 상태가 됩니다. 다음 시간까지 무기한 이 상태로 유지됩니다.

R' 입력에 LOW가 일시적으로 적용됩니다.

1. R'이 일시적으로 LOW가 되고 S'이 HIGH이면 G2의 출력이 HIGH가 됩니다.

2. G2의 출력이 HIGH이면 S'의 input이 HIGH이므로 G1의 출력이 LOW가 됩니다.

3. G1의 출력이 LOW이면 → G2. R' 입력의 LOW가 제거되더라도 Q' 출력이 HIGH로 유지되도록 합니다.

Q 출력이 LOW이면 래치가 RESET 상태가 됩니다. 이제 래치는 S' 입력에 순간적으로 LOW가 적용될 때까지 RESET 상태로 무기한 유지됩니다.

S-R Latch Truth Table Gated Latch

일반 latch에 enable 신호가 더 들어온 형태입니다.

enable 신호가 LOW면 입력이 무엇이 들어오든지 변화하지 않지만 HIGH면 입력에의해 출력이 control 됩니다.

여기서 invalid 상태는 enable, S, R 모두 1일때 발생합니다.

NAND D Latch / NOR D Latch D 의 input 과 EN input이 모두 HIGH이면 Latch는 set 상태가 됩니다.

D 의 input 은 LOW 그리고 EN은 HIGH이면 Latch는 reset 상태가 됩니다.

Flip-Flop

플립플롭은 latch와 비슷하지만 clock이라는 input이 새롭게 등장합니다.

clock은 간단히 말해 출력을 control 할 수 있는 신호 입니다.

Edge-triggered flip-flop

edge-triggered 플립플롭은 positive edge(rising edge) 또는 negative edge(falling edge) 로 변화시킵니다. 그리고 clock 변수의 변화에 따라 민감하게 반응합니다.

edge-trigger의 logic symbol을 확인하는 것은 위의 그림에서 C input 입니다. 이 삼각형 모양의 input은 dynamic input indicator라고 불립니다.

D Fllp-Flop

d flip-flop은 동기식 입력입니다. 왜냐하면 입력 데이터가 clock신호가 fallng edge 일때 출력에 의해 변화되기 때문입니다.

D가 HIGH 일때 Q 출력은 HIGH 이고 Flip-Flop은 set 상태입니다.

D가 LOW 일때 Q 출력은 LOW 이고 Flip-Flop은 reset 상태입니다.

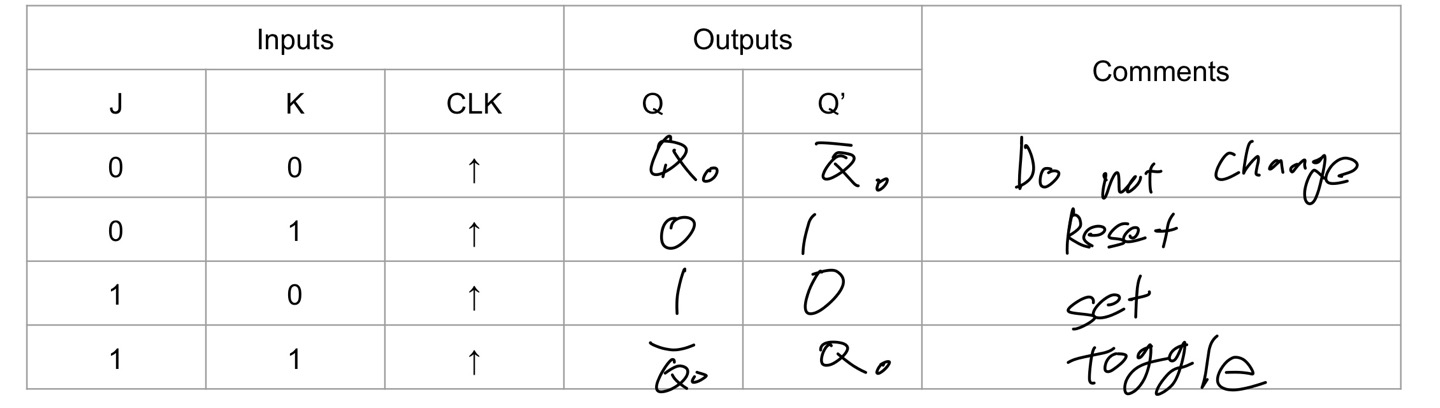

J-K Flip-Flop

J가 HIGH 이고 K가 LOW 이면 Q가 HIGH이되고 SET 상태가 됩니다.

J가 LOW 이고 K가 HIGH 이면 Q가 LOW가 되고 RESET 상태가 됩니다.

J와 K 모두 LOW 이면 출력은 이전출력에서 not change가 됩니다.

J와 K 모두 HIGH 이면 상태를 변화시킵니다. (toggle 모드)

JK Flip-Flop은 clock pulse의 triggering edge를 제외한 상태를 변화시킬 수 없습니다.

ex) Gated D Latch와 D Flip-Flop의 차이점

전자는 비동기식이고 후자는 동기식 입니다.

ex) J-K 플립플롭과 D 플립플롭의 기본적인 Operation 차이점

no change 와 toggle

'디지털 회로개론' 카테고리의 다른 글

Lecture 19 (Multiplexer & Demultiplexer & Parity Generator/Checker) (0) 2021.12.10 Lecture 18 (Converter) (0) 2021.12.10 Lecture 17 (Decoder & Encoder) (0) 2021.12.09 Lecture 16 (Comparator) (0) 2021.12.08 Lecture 14&15 (Adder) (0) 2021.12.06